Bespoke chips for drivetrains

STMicroelectronics has launched a family of microcontroller chips designed specifically for electrified drivetrains (writes Nick Flaherty).

The Stellar P microcontrollers are automotive qualified and combine the CAN-XL in-car comms standard to handle the demand for more real-time data with actuation functions.

The controllers are built on a 28 nm fully depleted silicon-on-insulator (FD SOI) process. This protects against radiation errors and provides lower power consumption, allowing higher junction temperatures of 165 ºC for use in the drivetrain with smaller heat sinks.

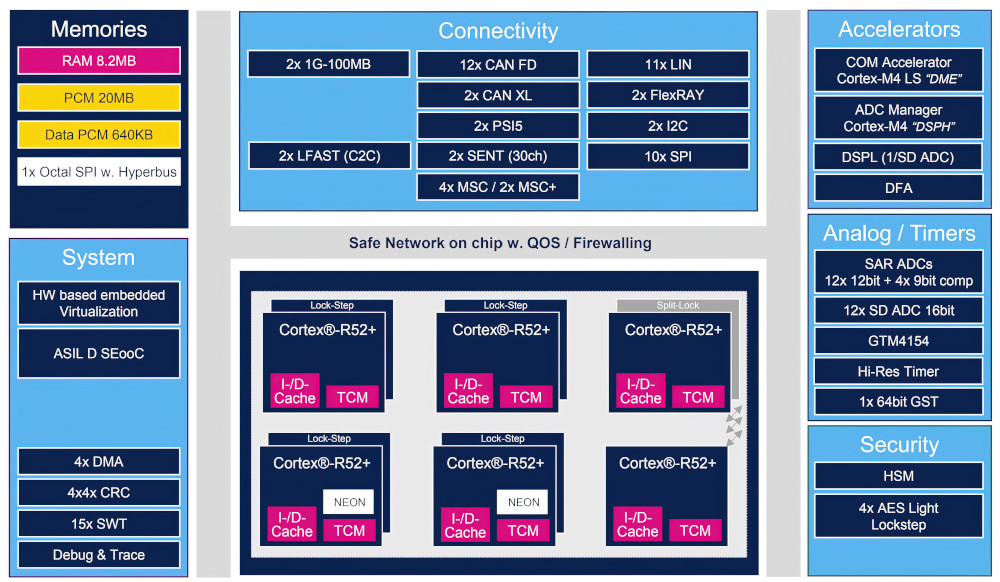

The family of chips has up to six Arm Cortex R52 processor cores, some operating in lockstep and some in split-lock mode to provide failsafe redundancy. The lockstep mode allows each processor to check on the activity of the others to ensure correct operation before moving to the next operation.

The lockstep also includes two Cortex‑M4 cores that act as multi-purpose accelerators to move data around, also in a lockstep configuration.

It supports ISO 26262 ASIL-D safety functions that are essential for drivetrain designs. In addition, the FD SOI technology inherently provides superior protection against system unavailability while ensuring compliance with the most stringent safety standards.

The microcontroller also supports hardware virtualization to run software in its own safe memory allocation, or sandbox. This is handled using features in the Cortex-R52 cores and firewalls to resource access. This simplifies the development and integration of multiple-source software on the same chip while ensuring safe isolation and performance and usually requires microprocessors rather than real time microcontroller cores.

The microcontrollers integrate up to two blocks of 20 Mbytes of Phase Change (non-volatile) Memory (PCM). This is made using a germanium antimony tellurium alloy, and takes advantage of rapid heat-controlled changes in the material’s physical property between amorphous and crystalline states.

The memory cell has a high resistance in the amorphous state (logic 0) and low resistance in the crystalline state (logic 1). The cell reads and writes at low voltage and provides faster access times than embedded flash memory, at lower power and with more reliable operation at high temperatures. It also supports the ability to overwrite a single bit, which is not possible with embedded flash memory, for faster writing of data.

The PCM also supports over-the-air (OTA) updates with no downtime, by using a new mechanism that dynamically allocates memory space to the new downloaded software image. This is held in the second 20 Mbyte block until it is validated, while the rest of the memory continues to execute the running application in real time from the first block. This avoids the risk of an OTA update failing and ‘bricking’ the microcontroller.

The FD SOI process supports fast analogue-to-digital (ADC) converters and embedded advanced signal processing, as well as dedicated sensor/actuator interfaces. The high-end devices have 12 separate 12-bit successive approximation (SAR) ADC blocks as well as two dual-channel 9-bit SAR converters with fast comparator mode, again to support ASIL D safety designs.

There are 12 other 16-bit sigma-delta ADCs, each with an embedded digital signal processor to pre-process the data. All of these are synchronised by an autonomous generic timer module.

The CAN XL protocol provides more than 2048 bytes of payload, including a 1-byte protocol type field indicating the content of the 4-byte address field and the 2048-byte data field. This allows the separation of frame priority and address information and supports data rates up to 20Mbit/s, up from 1Mbit/s in CAN and CAN-FD.

A CAN XL protocol also embeds some management information such as the virtual CAN (VCAN) field. This 1-byte field enables to run up to 256 channels on a single network segment.

A fast hardware security module, extended with cryptographic engines operating in lockstep, supports secure ASIL D functions and enables enhanced EVITA full security capability. It also provides high-speed security cryptographic services and safe network authentication to further protect manufacturers’ firmware as well as end-users’ data.

ONLINE PARTNERS